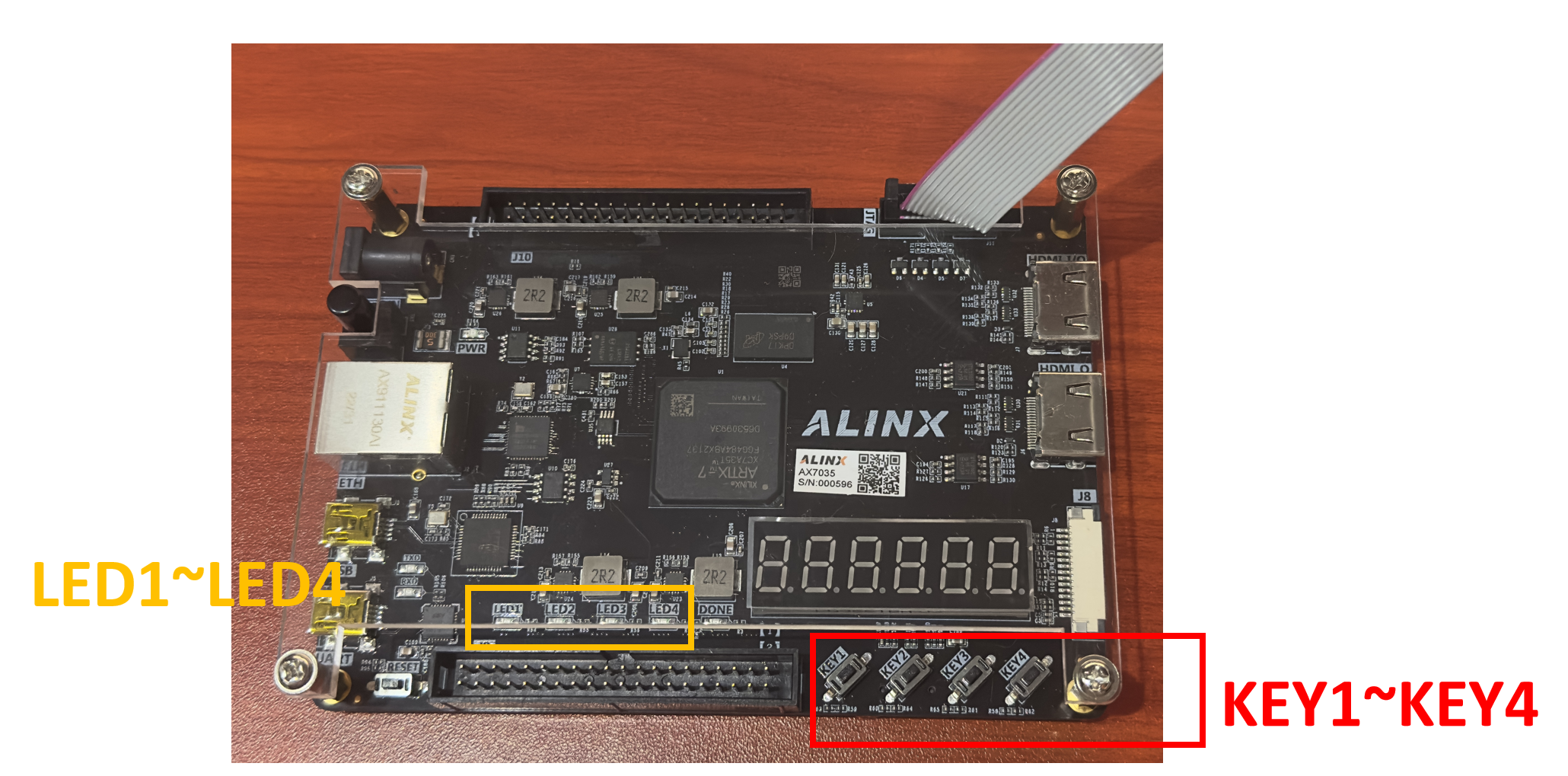

上电后/按下reset后,进入该状态,所有LED灯熄灭,

此时LED_mode = 4'b0000(LED_mode为Control Unit中流水灯工作模式寄存器,用以控制LED灯闪烁的逻辑)

初始静止模式同时按下KEY0~KEY3进入工作模式0,

或在工作模式0~3下,按下FPGA开发板上按键KEY1进入工作模式0,

此时LED_mode = 4'b0001,

在工作模式0下,开发板上的LED灯将按照下图所示的方式,做有规律的周期性流动:

LED0~LED4将依次闪烁,每个灯闪烁时长为1s,循环周期为4s

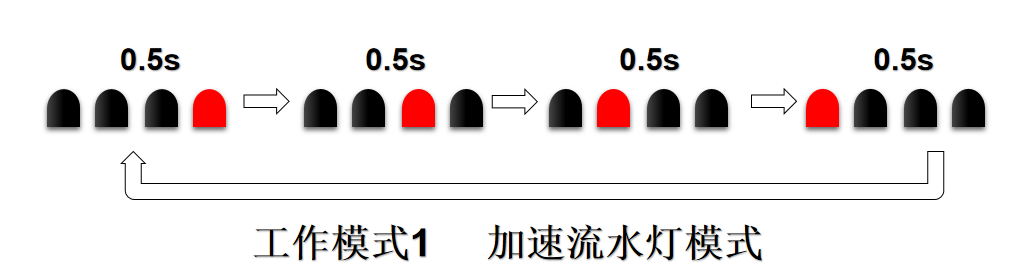

在工作模式0~3下,按下FPGA开发板上按键KEY2,进入该工作状态,

此时LED_mode = 4'b0010,

在工作模式1下,LED灯将加速流动,每个灯闪烁时长为0.5s,循环周期为2s:

!

在工作模式0~3下,按下FPGA开发板上按键KEY3,进入该工作状态,

此时LED_mode = 4'b0100,

该模式下LED等将模仿心跳的节奏进行闪烁(详见最后一章中FPGA运行视频)

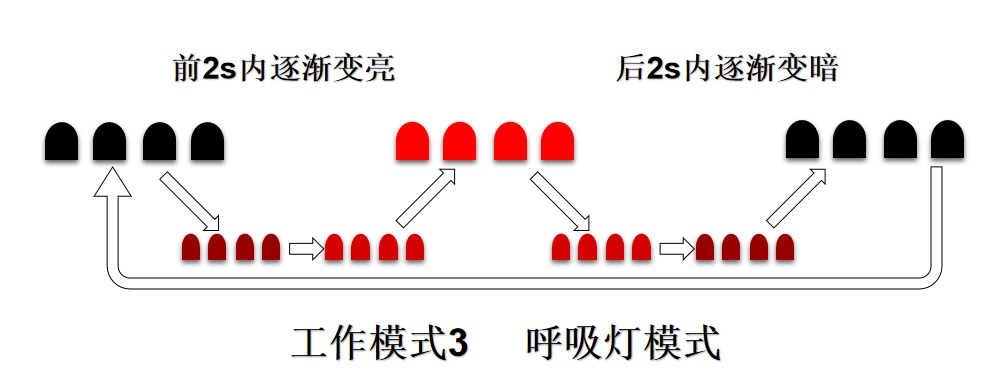

在工作模式0~3下,按下FPGA开发板上按键KEY4,进入该工作状态,

该模式下LED将周期性进行逐渐由亮到暗再到亮的变化(周期为4s,其中前2s由暗变量,后2由亮变暗),

此时LED_mode = 4'b1000,

由于FPGA开发板上的LED灯亮度无法直接配置,

该模式是通过调节LED灯的占空比来实现的,占空比越高,小灯的平均功率越大,我们人眼看到的亮度也就越高